# A Processor for ARX –Based Cryptography Algorithm with Side Channel Protection

# Mrs. Gopagoni Sandhya<sup>1</sup>, Dr. S. Lakshmi<sup>2</sup>

<sup>1</sup>Ph.D Scholar, Department Of Ece, Sathyabama University, Jeppiaar Nagar, Chennai, Tamilnadu, India <sup>2</sup>Professor, Department Of Ece, Sathyabama University, Jeppiaar Nagar Chennai, Tamil Nadu, India

## ABSTRACT

Arithmetic operations like addition, rotation, and logical operations exceptional or are the handiest elements for cryptographic algorithms which deploy on ARX. These are grouped to ensure passable confusion and diffusion homes. While ARX ciphers can undoubtedly be secured towards timing attacks, exquisite measures like protecting need to be thinking about a selected end goal to stop power and electromagnetic evaluation. This study affords processor architecture for ARX based cryptography that inherently guarantees first-arrange SCA opposition of any actualized calculation. This is carried out by making sure the whole facts way utilizing a Boolean concealing plan with three offers. We verify our safety asserts by way of mapping an ARX-calculation to the proposed architectures and utilizing the ordinary spillage reputation gadget in light of Student's t-check to make certain the aspect-channel competition of our processor.

Keywords: ARK, cryptography, rotational cryptanalysis.

# I. INTRODUCTION

Throughout the remaining a long time, our expertise of the term "security" has become a great deal Broader. In the start of cryptographic studies nearly the complete safety tough have become one manner or alternative narrowed down the on finding mathematical issues which might be difficult to clear up without the expertise of some thriller records or trapdoor function. As it grew to turn out to be out, physical structures are generally easier to attack thru the lower returned gate than via manner of attacking the mathematical approach that protects the front door. In specific, while an attacker has unrestricted get right of entry to a device—for example, due to the reality she is the holder of the tool or the tool is operated in a place which cannot often be secured physical assaults grow to be a severe chance. An unprotected hardware implementation famous its

secrets via, e.g., its strength consumption, the electromagnetic emanation, or an attacker may also want to even use needles to snoop on the chip internal facts exchange.

Protecting cryptographic hardware against bodily assaults is now for more than 15 years an ongoing studies difficulty depends. Many notable covering schemes had been proposed, but because of the feasible incidence of system faults as a result of the combinatorial commonplace feel in hardware, the safety of the covering schemes were risk.

Simon is a block cipher currently published through NSA as a light-weight possibility to the substantiallyused AES. Simon can be very promising for hardwareprimarily based embedded programs as its internal shape is quite easy and bit-orientated. Indeed, its authors show that the ASIC implementation of Simon calls for best 1234 GE (Gate Equivalent) for 128 bits of security, in comparison to 2400 GE for the smallest AES to date. Also, it turned into shown that a pieceserialized FPGA implementation of Simon units a present day location file with simplest 36 slices for 128 bits of protection, in comparison to 264 same slices for AES (in conjunction with the BRAMs) and 117 slices for Present. However, in an effort to truly enforce Simon on practical embedded platforms, protection in opposition to facet-channel evaluation must be taken under consideration. Side-channel evaluation (SCA) can break cryptosystems with the aid of exploiting vulnerabilities inside the realistic implementation of cryptographic schemes. SCA harvests the information leaked thru variations in the power intake, electromagnetic radiation, or execution time. Typically, the adversary builds a electricity model using a key speculation and compares the end result with the actual strength intake until the proper secret is determined. An SCA attack that is established the usage of a single hint is known as Simple Power Analysis (SPA), whilst an attack that mixes information throughout many traces at one-ofa-type inputs is called Differential Power Analysis (DPA). Attacks reading the number one 2d of a single factor inside the leakage trace are referred to as first order assaults. Higher order DPA attacks extract facts from the better order moments of 1 or greater leakage elements. However, higher order attacks be via higher noise degrees and consequently have a worse.

#### II. BACKGROUND

Referred quick present a unique co-processor subsystem this is designed as an Application-Specific Instruction-Set Processor (ASIP) for a particular magnificence of cryptosystems with inherent hardware resistance closer to aspect-channel evaluation. More precisely, our structure and training set follows ideas from the "Threshold Implementation" (TI) concept that is recounted to provide provable toward strength component-channel protection evaluation. As an ASIP it could be loaded with software program implementations of various

symmetric ARX-based cryptographic primitives, which includes circulation and block ciphers or hashabilities without the want for adaption of the hardware. We display that a prototype of our layout together with a software application implementation of Speck is not handiest pleasant in opposition to firstorder aspect-channel evaluation and timing assaults however can be realized at slight fees which can be even similar towards pure (included) hardware implementations. Note that the hardware is designed to sincerely counter the aforementioned aspect channel attack which appreciably relaxes the necessities for software engineers to cope with complex constraints of physical facet-channel safety. Display how a famous motive ALU format may be secured towards first-order passive physical attacks. Therefore, the functionality of a regular ALU is taken into consideration and its capability is transformed step-via-step for you to meet the requirements of the threshold implementation scheme. The figures [2] offers a committed accelerator for ARX-based cryptography, which does no longer consist of a attention on physical attacks. Finally, we are searching for advice from the proposals for issuechannel resistant (hardware) implementations of ARX-based totally absolutely structures as said in [3], [4].

#### **III. PRELIMINARIES**

# ARX algorithm :

ARX, standing for Addition/Rotation/XOR, is a category of symmetric-key algorithms designed the usage of handiest the following simple operations: modular addition, bitwise rotation and extraordinary-OR. In evaluation to S-field-primarily based designs, wherein the best non-linear factors are the substitution tables (S-boxes), ARX designs depend upon modular addition because the best supply of non-linearity. Notable representatives of the ARX magnificence consist of the stream ciphers Salsa20. For the cited algorithms, the choice of the usage of the ARX paradigm become primarily based on three observations. First, casting off the table lookups, associated with S-Box based totally designs, will

increase the resilience against aspect-channel attacks. Second, this layout approach minimizes the whole wide variety of operations accomplished for the duration of an encryption, allowing especiallyspeedy software program implementations. Finally, the computer code describing such algorithms may be very small, making this method in particular appealing for light-weight block ciphers wherein the reminiscence necessities are the most harsh.

Speck is an ARX ("add, rotate, XOR") layout-its nonlinearity comes from a modular addition, and it uses XOR and rotation for linear blending. Modular addition is an herbal preference over Simon's bitwise AND for software program performance: on the equal computational charge, it's stronger cryptographically. Indeed the ARX advent has a tendency to yield the brilliant appearing software program software algorithms. On an ASIC, modular addition can be achieved serially the use of asingle complete adder. While this on my own does no longer guarantee that lavout may also an ARX have compact implementations, undertaking this became a layout purpose, and such implementations of Speck can in truth be realized. While computation of the addition convey chain means that latency can be especially immoderate, this isn't always a trouble for lots lowgive up systems, wherein even a 64-bit addition can be executed in a single clock cycle. Furthermore, latency can be reduced on the price of place thru a ramification of nicely-advanced strategies (bring-look adders, deliver-select adders, and many others.) FPGAs commonly tend to include extraordinarily optimized circuitry for modular additions; this means that ARX designs ought to have very excessive basic performance on those systems as well.

### Side channel algorithm:

As explained inside the advent, SCA is a immoderate chance to any cryptographic implementation making the combination of appropriate countermeasures critical. Most of the typically diagnosed techniques are both protecting or hiding schemes. While hiding countermeasures try to lessen the sign-to-noise ratio [10], masking is predicated at the randomization of intermediate values to make the leakage unbiased of the call of the game values as much as a positive diploma [11]. Masking schemes are based totally on a legitimate theoretical basis and may provide provable safety as much as a positive order. In unique, the intermediate values are break up into a couple of shares and an adversary desires to combine leakages of a couple of these shares to get better the unshared price. This belief of attack is denoted as excessive reorder attacks. A protecting scheme of orderd affords provable protection toward all assaults of orders lower than d + 1 and it calls for a d+1-order attack to break it. Given a enough stage of noise inside the measurements, the complexity of an assault will increase exponentially in its order, as an awful lot as the component that it will become unfeasible in exercise. However, to offer this level of protection protecting schemes depend upon certain assumptions. If the ones assumptions are violated, the extent of security can be critically reduced. Therefore, it is important to enforce a masked set of rules with specific care. Notably, system faults, which can be temporary defective states, are a trouble for masked circuits and render а truthful hardware implementation of a covering scheme insecure [12]. Threshold Implementation: A normally used concept to gain comfortable masking within the presence of machine faults is Threshold Implementation (TI). One assumption of TI is uniformly shared inputs for every shared function. Since the outputs of these capabilities are commonly inputs to every different shared characteristic, it's far suited that the output of this type of characteristic is also uniform. This can be done by means of way of cautiously building the issue capabilities or with the addition of clean randomness.

#### **IV. PROPOSED WORK**

The work supplied on this paper is the layout of a common and essentially blanketed with the aid of a SCA. By updating the code, it follows ARX algorithm. So, this doesn't adapt any hardware layout. Merging of TI counter measures to spark is essential factor

rather than applying structure to chipper implementation.

linear. The production of a TI-conform shared representation of the addition is non-trivial.

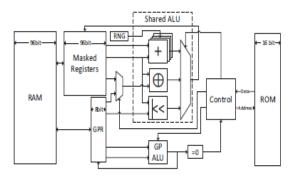

For this cause, we designed a application particular CPU (ASIP) with a TI-covered ARX-ALU this is probably cozy in opposition to first-order attacks (the use of d = 3 shares). Certainly, better-order assaults also can be avoided thru growing d at higher hardware costs. Our device is designed to break up any (SCA-critical) statistics flow from the control go with the flow. The fourfold pipelined structure is primarily based on a RISC technique and includes two separate ALUs. The aspect-channel blanketed ALU performs all important ARX operations on a included check in report with direct get right of entry to a source of randomness this is required for the addition operation. We in addition identified that a devoted unprotected ALU, which operates on a committed sign up report, is useful to increase the general overall performance at reasonable fees. Load and keep commands are available for shifting data among the RAM and the check in documents. The immoderate-stage shape of SPARX is supplied in Figure 1.

Fig. 1. High-Level Block Diagram of SPARX

The fundamental ALU operates on triple-shared 32bit phrases and is used for all calculations at the sensitive kingdom of the implemented ciphers. It includes a TI-blanketed adder, a xor and a rotation unit and is attached to a dedicated register report. Because every, the xor and rotation operations are linear, ensuring that every percentage is processed independently is sufficient for the masked implementation. However, addition in Z232 is nonThe trouble is referred in [13]. The one-of-a-kind styles of adder circuits are proposed for Booleanmasked TI primarily based values. We use a similar version in their concept based totally at the ripplebring adder as it's far an extended manner greater place-inexperienced for light-weight software than their presented Kogge-Stone adder, even as best requiring four bits of clean randomness in line with operation. In addition, we found that a moderate change of the precise blinded addition circuit can enhance the versatility of our processor. More precisely, in [13] the additions handiest Take the two summands as input and no preliminary deliver. However, it's far without problems possible to tweak the specific format to encompass this capability without breaching the safety assumptions. To this give up, we require that the enter supply is uniformly shared, this is implicitly given if it's far the output bring of a preceding addition. As the output carry stocks aren't unbiased in their associated sum bits they need to not be used as joint inputs to a shared feature. Our design debts for that via handiest the usage of the deliver bits for adding multiple 32-bit block. With this tweaked adder, our processor can guide multi-precision addition of inputs massive than 32 bits (e.g., for Speck128/256, Blake2b or Three fish) without negatively affecting the overall performance of the single-limb 32-bit addition.

The adder consumes 32 cycles to complete 32 additions, which indicates that it's far the slowest adder on this layout. To provide high throughput the clock is greater with excessive frequency with the aid of doubling the primary clock. This ends in installation in postpone by using decreasing to sixteen cycles. The retrieve operation doesn't take into account about the operation it simply gives the modern nation. This is the most effective one operation which offers statistics that the retrieve operation after each sixteen cycles. This mission is trivial and may without problems be automated due to the fact in each cycle exactly one new guidance is fetched. Parallel addition operations are instanced for excessive through put, which reduces the average quantity of required cycles. Incorporating more than 4 adders offers diminishing returns in overall performance and couldn't be efficiently exploited with the aid of most ARX algorithms.

SPARX incorporate unprotected 8 bit Arithmetic and logical unit which performs mathematical and logical operations with high performance. This gives all single cycle operations. For controlling cause this auxiliary ALU is used without occupying the primary adders. It also can adequately calculate round constants and different inputs to the cryptographic set of rules. Easily corrupted statistics can't be locked and particularly included via ALU. Unmasked values are loaded and saved in RAM to allow top interplay. This is useful to dynamically choose a cipher set of policies or to generate an "encryption-executed" flag for an outdoor major CPU.

Data and control waft is attained by SPARX. This is designed by means of considering trendy RISC architecture. It follows the 4 staged pipelines. As it relies upon on single cycle, it makes use of information or guidance. The shape does no longer encompass a stack or call and go back operations to allow characteristic calls, as cryptographic primitives do now not advantage from this in cutting-edge. It does, however, useful resource branches and loops which can reduce the code length for roundprimarily based absolutely algorithms - like ARX ciphers - extensively. In order to manipulate this system drift, branching operations are carried out: an unconditional soar and a branch-not-zero (bnz) education. The situation for the bnz education is generated by using the use of comparing the quit result of the overall reason ALU operations to 0. Masked facts cannot be used as enter to this system, which ensures that the execution times of all programs going for walks on the proposed structure are statistics impartial, rendering the design resistant to timing-assaults. In give up, there are not any operations that stall or flush the pipeline, which results in a throughput of one education in step with cycle.

Our SPARX processor depends on a Harvard structure, i.e., it has as isolated programming and measurements memory. This permits ventured forward preparing throughput without requiring another memory port and neatly permits lovely widths for certainties and preparing words. Each tutoring word is encoded in 16 bits so a product memory of the indistinguishable width can without issues offer one direction with regards to cycle. The utility memory length is restricted to 4096 terms. For evaluation, our executions of Speck and Salsa20 need 113 and 310 direction terms separately. The data port width is ninety six piece to locally help get right of access to 32-bit conceal values. Just immediate tending to of RAM records is bolstered. The measure of RAM isn't steady anyway the direction expression width constrains its term to 512 96-bit phrases. Other than for buffering information, the RAM is moreover utilized as IO interface. With a specific end goal to enhance the throughput even as keeping the measure of pipeline degree genuinely low, the processor has get right of passage to devoted registers. In any case, it's far basic to disengage the veiled touchy insights from the unmasked gigantic reason records that license you to spare you certainties spillage. To this surrender, isolate test in reports have been executed in the proposed engineering. The 8 in mode reason registers are 8bit wide and might be utilized for putting away pivot counterbalances, round constants, counters or banners. The second enroll document is utilized as a working memory for the delicate records words SPARX is strolling on which fuses the key, the plaintext and the figure literary substance. The assortment of shared registers must be considered painstakingly because of the reality each sign in is ninety six piece tremendous and subsequently sumptuous in expressions of equipment things. Keeping in mind the end goal to augment the use of the 4 adders, up to eight operands/registers are most extreme fitting. While some ARX-calculations need

to pick up from more prominent than 8 enrolls, the more noteworthy equipment rate does never again pay off for generally circumstances.

Keeping in mind the end goal to verify SCA-security for subjective ARX usage, data drift from the covered data to the unprotected assistant information should be precluded. Something else, records might be spilled in spite of the truth that the ARX-natives had been safely executed. This is guaranteed by means of instantiating separate registers for the essential covered data and the assistant non-veiled data. The secured xor module works on each covered qualities or one covered and one non-veiled information. In every time conceal yield esteems are created. This capacity can impressively improve general execution for calculations depending on round constants: Because the constants are open and don't should be secured they might be registered the utilization of the general reason ALU rather than the slower, more prominent limited ARX ALU. The xor of the nonconceal esteem B and the common value  $A = A1 \bigoplus A2$  $\oplus$  A3, that is inside spoken to on the grounds that the triple  $A^{\sim} = (A1, A2, A3)$ , is figured as  $A^{\sim} \oplus B = (A1, A2, A3)$ A2, A3 $\oplus$  B). The obstruction of SPARX contrary to SCA isn't hurt amid this activity as a result of reality best one extent of the covered cost is changed by utilizing the direct and invertible xor highlight. For the pivot, the rate to turn is constantly concealed even as the revolution balance is non-veiled. This isn't an issue insofar as the counterbalance does now not rely upon riddle records. Keeping measurements spill out of the veiled to the non-conceal information through basic memory motivate passage to isn't upheld in equipment. Consequently, the compiler should guarantee that tricky records is not the slightest bit stacked into non-conceal registers.

### V. RESULTS AND CONCLUSION

While, to our knowledge, the proposed design is the first side-channel resistant, flexible ARX accelerator, several hardware implementations of ARX ciphers have been introduced in the literature. Compared to previous architecture the proposed architecture gives more security for side channels, i.e.it protects more in side channels. Along with this the data protection can be done for more number of bits.

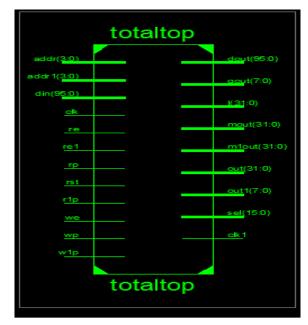

Figure 2. Block diagram

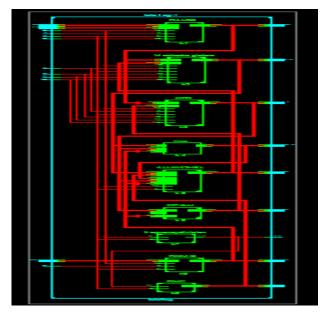

Figure 3. RTL schematic diagram

|                       |            |    |                                        |          |      |          |       |          |          | 1,251.20   | 0 ns     |

|-----------------------|------------|----|----------------------------------------|----------|------|----------|-------|----------|----------|------------|----------|

| Name                  | Value      | .  | l, 160 ns                              | 1,180 ns |      | 1,200 ns | Lini  | 1,220 ns | 1,240 ns |            | 1,260 ns |

| l <mark>a</mark> re   | 0          | Ť  |                                        |          |      |          |       |          |          |            |          |

| l🔓 re1                | 1          |    |                                        |          |      |          |       |          |          |            |          |

| ▶ 📑 addr[3:0]         | 0          |    |                                        |          |      |          | 0     |          |          |            |          |

| լե տե                 | 0          |    |                                        |          |      |          |       |          |          |            |          |

| Ц гр                  | 0          |    |                                        |          |      |          |       |          |          |            |          |

| 🔓 w1p                 | 0          |    |                                        |          |      |          |       |          |          |            |          |

| ll <mark>a</mark> r1p | 1          |    |                                        |          |      |          | L     |          |          |            |          |

| 🕨 📲 addr1[3:0]        | 4          |    |                                        | 3        |      |          | χ     | 4        |          |            | 2        |

| 🕨 📲 dout[95:0]        | 0000001110 |    | C0000011100000000000000000000000000000 |          |      |          |       |          |          |            |          |

| 🕨 📲 mout[31:0]        | 00010efe   |    |                                        | fffffe   |      |          | χ     | 00010ef  |          |            | 00000    |

| ▶ 📲 m1out[31:0]       | 00010efe   |    |                                        | fffffe   |      |          | χ     | 00010ef  |          |            | 00000    |

| 🕨 📲 gout[7:0]         | 00         |    |                                        |          |      | 01       |       |          |          | (          | 10       |

| 🕨 🕌 I[31:0]           | 00004000   |    | 00001000                               |          |      | 0000     |       |          |          | X 00004000 |          |

| 🕨 🐳 out(31:0)         | 00000000   | D  | 00010efe                               | X        | 0001 | 1efe     | 00022 | 000      | 0000     |            | 00000    |

| ▶ 號 out1[7:0]         | 00         |    |                                        | 01       |      |          |       |          | 00       |            |          |

| ling dk1              | 0          |    |                                        |          |      |          |       |          |          |            |          |

| 🕨 📲 sel(15:0)         | 72         |    |                                        | 36       |      |          |       |          | 72       |            |          |

|                       |            | X1 | : 1,251.200 ns                         |          |      |          |       |          |          |            |          |

Figure 4. Output waveforms

In this paper presents a flexible ARX-ASIP that essentially protects all implemented algorithms against timing and first-order side-channel attacks. The well established leakage scheme is applied for practical demonstration of resistance.

block cipher, stream ciphers and hash functions are done at same time and updated by cryptography using proposed multiple ARX algorithms .By changing minimal requirements securely data is adapted.

#### VI. REFERENCES

- R. Beaulieu, D. Shors, J. Smith, S. Treatman-Clark,

B. Weeks, and L. Wingers, "The SIMON and SPECK Families of Lightweight Block Ciphers.," IACR Cryptology ePrint Archive, vol. 2013, p. 404, 2013.

- [2]. A. Moradi, A. Poschmann, S. Ling, C. Paar, and H. Wang, "Pushing the Limits: A Very Compact and a Threshold Implementation of AES," in Advances in Cryptology EUROCRYPT 2011 (K. G. Paterson, ed.), vol. 6632 of Springer LNCS, pp. 69–88, 2011.

- [3]. A. Aysu, E. Gulcan, and P. Schaumont, "SIMON Says: Break Area Records of Block Ciphers on FPGAs," Embedded Systems Letters, IEEE, vol. 6, pp. 37–40, June 2014.

- [4]. T. Good and M. Benaissa, "AES on FPGA from the Fastest to the Smallest," in Cryptographic

Hardware and Embedded Systems CHES 2005 (J. Rao and B. Sunar, eds.), vol. 3659 of Springer LNCS, pp. 427–440, 2005.

- [5]. P. Yalla and J. Kaps, "Lightweight Cryptography for FPGAs," in International Conference on Reconfigurable Computing and FPGAs, 2009. ReConFig '09., pp. 225–230, Dec 2009.

- [6]. S. Bhasin, T. Graba, J.-L. Danger, and Z. Najm, "A look into SIMON from a sidechannel perspective," in IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), 2014, pp. 56–59, May 2014.

- [7]. D. Shanmugam, R. Selvam, and S. Annadurai, "Differential Power Analysis Attack on SIMON and LED Block Ciphers," in Security, Privacy, and Applied Cryptography Engineering (R. Chakraborty, V. Matyas, and P. Schaumont, eds.), vol. 8804 of Springer LNCS, pp. 110–125, 2014.

- [8]. S. Nikova, C. Rechberger, and V. Rijmen, "Threshold Implementations Against Side-Channel Attacks and Glitches," in Information and Communications Security (P. Ning, S. Qing, and N. Li, eds.), vol. 4307 of Springer LNCS, pp. 529–545, 2006.

- [9]. B. Mazumdar, S. S. Ali, and O. Sinanoglu, "Power analysis attacks on ARX: an application to Salsa20," in IOLTS, pp. 40–43, IEEE, 2015.

- [10]. N. Veyrat-Charvillon, M. Medwed, S. Kerckhof, and F. Standaert, "Shuffling against side-channel attacks: A comprehensive study with cautionary note," in ASIACRYPT, vol. 7658 of Lecture Notes in Computer Science, pp. 740–757, Springer, 2012.

- [11]. E. Prouff and M. Rivain, "Masking against side channel attacks: A formal security proof," in EUROCRYPT, vol. 7881 of Lecture Notes in Computer Science, pp. 142–159, Springer, 2013.

- [12]. S. Mangard, N. Pramstaller, and E. Oswald, "Successfully attacking masked AES hardware implementations," in CHES, vol. 3659 of Lecture Notes in Computer Science, pp. 157–171, Springer, 2005.

- [13]. A. Poschmann, A. Moradi, K. Khoo, C. Lim, H. Wang, and S. Ling, "Side-channel resistant crypto for less than 2, 300 GE," J. Cryptology, vol. 24, no. 2, pp. 322–345, 2011.